Hardware testing has never been this easy.

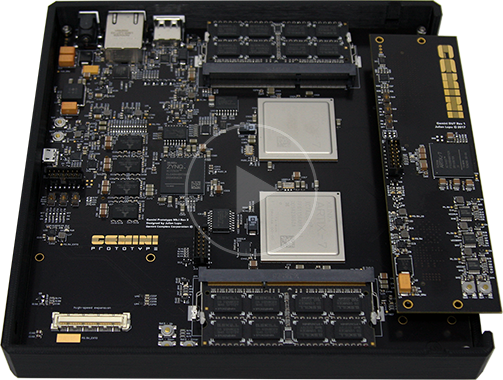

The Gemini Stimdeck can execute thousands of test patterns by reading and writing logic levels on the Gemini Test Bus, to functionally test any attached device.

Design custom mezzanine boards that can easily interface to the Gemini Test Bus.

Step 2.Develop test patterns to functionally test your specific hardware devices-under-test.

Step 3.Using the Gemini Web App, easily execute thousands of test patterns and get pass or fail feedback immediately.

Develop test patterns using a simple vector format.

Dots is a simple language that allows you to define the pins of your device-under-test, and then drive and expect logic levels on those pins. You can create programs to configure a JTAG TAP controller, program an FPGA, or interact with your custom silicon.

Dots programs are compiled using Leda into a binary format that can be executed by the Gemini Stimdeck.

→ see more

# test a register scan chain

Pins CLK, RESET_B, IN, OUT

# assert reset_b

VC0XX

VC10X

# sea of zeros

repeat 10 VC10L

# one in sea

VC11L

# check zeros

repeat 9 VC10L

# now check high

VC10H

Create powerful test programs using the power of Lisp.

Create powerful test programs to execute thousands of test patterns and conditionally branch and control the flow of execution as needed. As programs run, execution gets logged so you can see the progress in real time using the Web Interface.

→ see more

# run jtag boundry scan test

(set-profile "board_profile.json")

(run

(load "init_jtag.s")

(load "boundry_scan.s")

(load "finish_jtag.s"))

Tech Specs

| Test Bus I/O | 400 digital channels |

|---|---|

| Vector Execution Speed | 50 Mbps |

| Per Channel Vector Burst Depth | 67M vectors |

| Latency | sub 10 nanosecond latency |