Quick Downloads

The Gemini Stimdeck is a triple-fpga device that runs VecOS, an operating system designed specifically to execute test patterns. The tester features a 400 pin external I/O bus that can interface to any device-under-test, through custom designed mezzanine boards.

The Gemini Stimdeck is managed by a Xilinx Zynq-7000 SoC called Agent, that orchestrates the entire boot process and runs meta-level processes. It configures and communicates with two Xilinx Artix-7 FPGAs, named Castor and Pollux, that run the Gemini Vector Processing Units (VPUs), which are specially designed processors that execute compiled DOTS test patterns called Stim files. Each Artix-7 FPGA has its own 8GB of DDR3 tester memory, that is used to store and execute the compiled Stim file test patterns.

Agent is reponsible for serving a front-facing web application, that provides a simple user interface, so you can upload test program prgm files and precompiled stim binaries over NFS. With the click of a button, you can queue prgm files to run. Agent continuously monitors the queue and executes the test programs, as slots open up. Upon completion, the pass/fail results of all Stim file executions are recorded in the on-board database, and available for you to see through the web app.

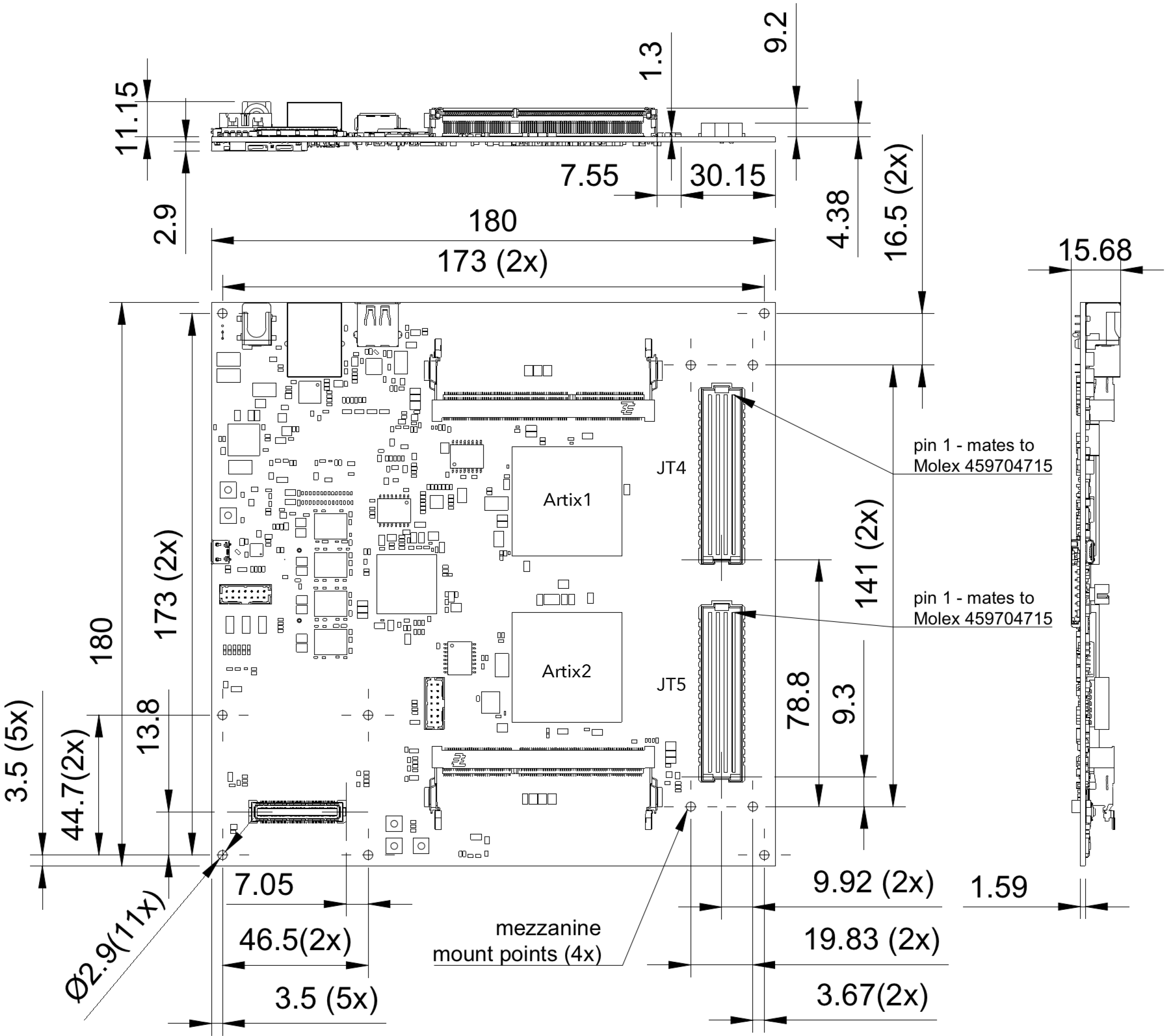

Mechanical Drawing

Below is a mechanical drawing of the Gemini Stimdeck. Reference the drawing when designing your DUT Board PCB.

Important: please check that the total mating height of the Gemini Stimdeck with the DUT board does not exceed your design requirements.